## **Description**

Magillem Design Life Management (MDL) delivers advanced functionalities on top of Magillem Platform Assembly (MPA) to address today's challenges of complex SoC assembly with aggressive time-to-market constraints:

- Incremental releases of the same IP: an internal or external IP provider can help an integrator smoothly use new versions of his IP (delivered following bug fixes, spec changes, or interface updates), at any stage of the integration work

- Integration of revisions of the same IP, or IP changed with a specification spec change: an integrator can easily replace one IP version with another, with automatic update of existing connections/IP configuration

- ECO feature: after RTL freeze, rebuild the frozen IP boundary once it has been updated, using a wrapper

- Joined integration on same levels: multiple users work in parallel on the same complex design, and how to merge their contributions while preventing conflicting changes

- Replicate a design update to a design branch: incremental changes on a given project can be replicated into a derivative project

- Facilitate script creation from an existing platform: to replace manual assembly work by automated steps, just by exporting the current design

- Align XML bus usage: automatic updates of all bus Type and abstraction Type references.

MDL provides multiple scalable solutions to address these issues, which have been proven in production by major companies on complex IP-XACT platforms: IP Update, Design diff and merge, and design2script.

The IP Update feature benefits to both IP providers and integrators. The user-friendly diff GUI pinpoints differences between 2 IP-XACT component descriptions, which impact its later integration (for example, change on port name or size, interface update, modified parameters or IP views). In same diff GUI, an IP provider or integrator can easily define specific rules to apply during update of existing IP configured and connected instances. Based upon these rules, an integrator can launch an automated and correct-by-construction process will perform replacement of all selected IP instances at any level of hierarchy in the platform.

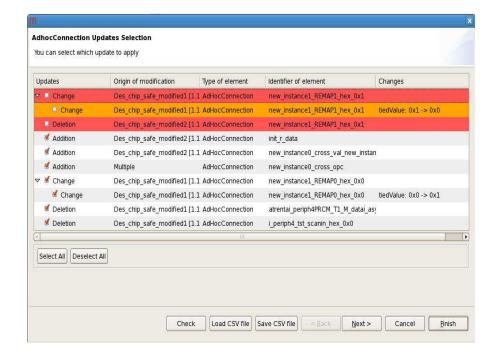

To address parallel work performed by multiple users on same platform, the design diff GUI/TCL highlights any conflicts or major modifications and help initial integrator in their resolution, either by accepting/rejecting them, or by performing selected operations (port or instance renaming for example). Based upon these choices, the merge engine will create the resulting IP-XACT platform.

Finally, the design2script feature produces the corresponding script for a selected IP-XACT platform. This script can later be modified to recreate a derivate platform or as a basis to automate a set of connections/instantiations for example.

## **Features**

- Comprehensive Diff GUI to visualize all IP modifications which impacts later integration

- SoC Realization

- Possibility to define update custom rules in case a port/parameter/interface/view has been modified between 2 versions of an IP

- Automatic update of all or a selection of IP instances at all hierarchical levels of a platform, based on the same custom or automatic rules

- Design Diff GUI showing conflicting changes and major modifications, performed on same design/hierarchical component by multiple users in parallel

- Possibility to accept/reject any changes and resolve conflicts, directly in Diff GUI

- Powerful and scalable merge engine

- Correct-by-construction processes and pre-check phases prevent design corruption

- Align bus and abstraction VLNV

- Recognition of interface connection

- Available in GUI and in TCL API

- Support both IP-XACT 1.4 and IEEE 1685 versions

## **Benefits**

#### To the IP provider:

- Review of IP changes between 2 different versions

- Generation of custom rules for later automated integration of new IP versions

#### To the IP/SOC integrator:

- Assessment of IP modifications before integration

- Automated IP update of all or a selection of IP instances

- Diff and merge of parallel modifications on same design

- Support of automated derivative designs

### To the Project lead:

- Reduce iteration cycle time for integration of new IP versions, at any stage of the assembly

- Enable split of assembly work between multiple users to achieve shorter design release cycle, or skill based design update (functional, design for test, clock, reset, analog, digital)

# **Specifications**

| Specifications                                                                                 |   |

|------------------------------------------------------------------------------------------------|---|

| MDL FEATURES                                                                                   |   |

| IP-XACT compatibility                                                                          |   |

| IP-XACT 1.4 certified                                                                          | x |

| IP-XACT IEEE1685 certified                                                                     | x |

| Execution modes                                                                                |   |

| GUI mode                                                                                       | x |

| TCL/Ruby/Python API execution                                                                  | x |

| IP Update                                                                                      |   |

| Comprehensive Diff GUI                                                                         | x |

| User mapping rules definition to apply during IP Update                                        | x |

| Automatic tie connection generation on new ports                                               | x |

| Automated Correct-by-construction IP-XACT platform update at any level of hierarchy            | x |

| Component instance view update                                                                 | x |

| Support instance updates for Interface/port/parameter renaming/resizing/deletion/merging       | x |

| ECO feature: after RTL freeze, preserve pinout, use spare ports for additional signal crossing | x |

| IP migration                                                                                   | x |

| Automatic alignment of Bus and Abstraction used a user defined list                            | x |

| IP-XACT object migration from an old version of ip-xact to a more recent one                   | x |

| Automatic recognition of interface connections from low level point to point adhoc connections |   |

| Design diff and merge                                                                          | x |

| Comprehensive Diff GUI showing concurrent conflicts/changes on same IP-XACT platform           | x |

| Accept/Reject any change                                                                       | x |

| Conflict resolution wizard (choice selection, instance renaming)                               | x |

| On-the-fly checks to verify the validity of choices/conflict resolution                        | x |

| Powerful and scalable diff engine (2way-3way)                                                  |   |

| Design 2 script                                                                                | x |

| IP-XACT design export into TGI script                                                          | x |

| IP-XACT design export into Magillem TCL API script                                             | x |

| IP-XACT design export into Magillem TCL RTL API script                                         | x |

|                                                                                                |   |

|                                                                                                |   |

Email: contact@magillem.com Web: www.magillem.com

USA Magillem 2225 E. Bayshore Road Palo Alto, CA 94303 Tel: +1 (408) 214 2842

Europe

Magillem

251 rue du Faubourg Saint-Martin

75010 Paris - France

Tel: +33. (0)1.40.21.35.50